Hi @ymj

Like almost any other interface, the chip select must be active before the data starts to arrive. If the chip select was to go active slightly after the data (say by 1ns), then the device receiving the information would have no idea that the information is intended for that device. if the chip select was to go active at exactly the same time as the data, then the receiving device might still miss it, due to delays in the wiring or in the transmitting and receiving circuitry.

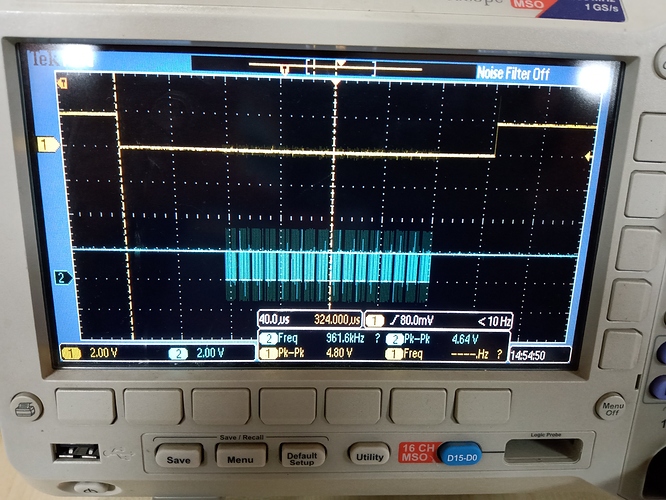

In order to ensure that the receiving device knows that information is intended for that device the chip select must go active well in advance of the data. In this case (and with every SPI chip I have ever used) “well in advance” is one clock time.

Same problem at the end of the data, if the chip select goes inactive too soon the receiving device might miss the data.

Here is a fragment from a typical SPI device datasheet.

As you can see the chip select must go active tcssc = 100nS before the the clock. The clock period tsclk is 250ns, this means that the chip select must go active about 1/2 clock time before the data, and every controller rounds this up to a full clock cycle. Same thing with tsccs at the end of the cycle.

Without the one clock before and after the data the SPI bus wouldn’t work.